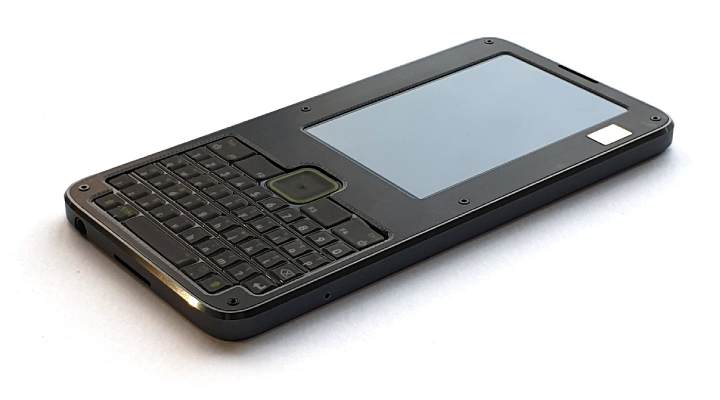

Sutajio Kosagi Precursor

mobile/sutajiokosagi/precursor (platform)

| Property | Description |

|---|---|

| Manufacturer | Sutajio Kosagi |

| Model | Precursor |

| Year | 2021 |

| Max CPU | Integrated VexRiscV |

| Max RAM | 16 MB Onboard off-chip SRAM. Used in addition to 128 KB on-chip SRAM. |

| Image | Precursor, credit Sutajio Kosagi (https://media.telefonicatech.com/telefonicatech/uploads/2023/10/precursor-huang-bunnie-device.jpg) |

| Software: User-Facing Environment | Free |

| Software: Operating System | Free (Xous) |

| Software: Bootloader/Recovery | Free (loader) |

| Firmware: Persistent Privileged Code (e.g. x86 SMM) | RISC-V, nothing akin to x86 SMM |

| Firmware: Late Boot/Payload | No FW except bootloader/BROM |

| Firmware: Platform Initialization | Free |

| Firmware: Memory Initialization | Free |

| Firmware: Early Boot (incl. RoT) | No FW except bootloader/BROM |

| Firmware: Boot ROM | Free |

| Firmware Signing | Available, user-controlled |

| CPU Microcode | ucode for ed25519 engine |

| Management Coprocessor: Firmware | None or N/A - feature/system not present |

| Communications Coprocessor: Internal Firmware | Proprietary (WF200 WLAN) |

| Communications Coprocessor: Host-Loaded Firmware | Proprietary, can disable WLAN |

| Security Coprocessor: Firmware | Free (FPGA crypto engine) |

| Embedded Controller: Firmware | Free (betrusted-ec) |

| Hardware: Board Electrical Schematic | Free |

| Hardware: Board PCB Design | Free |

| Hardware: CPU Instruction Set | Free (RISC-V) |

| Hardware: CPU/SoC Implementation | Free soft core, prop. FPGA (FPGA, VexRISC-V) |

| Hardware: CPU/SoC Synthesis Toolchain | Free for EC, prop. for main core |

Back to Table