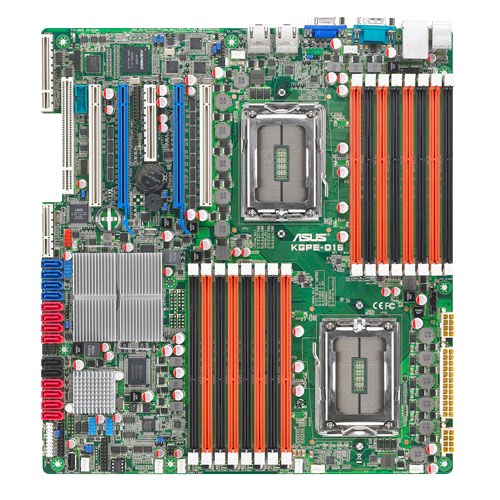

ASUS KGPE-D16

server/asus/kgped16 (platform)

| Property | Description |

|---|---|

| Manufacturer | ASUS |

| Model | KGPE-D16 |

| Year | 2010 |

| Max CPU | 2x AMD Opteron 6386 SE |

| Max RAM | 512GB, possibly 1TB 16x32GB DDR3-1600 ECC RDIMM. 16x64GB (for 1TB) may also be possible but is untested. |

| Image | KGPE-D16 image credit ASUS (https://www.asus.com/media/global/products/4AUqWniKqYByIAxw/P_setting_fff_1_90_end_500.png) |

| Software: User-Facing Environment | Free |

| Software: Operating System | Free |

| Software: Bootloader/Recovery | Free |

| Firmware: Persistent Privileged Code (e.g. x86 SMM) | Free (Coreboot) |

| Firmware: Late Boot/Payload | Free (Coreboot) |

| Firmware: Platform Initialization | Free (Coreboot) |

| Firmware: Memory Initialization | Free (Coreboot) |

| Firmware: Early Boot (incl. RoT) | Free (Coreboot) |

| Firmware: Boot ROM | None x86 CPUs don't have true "software" boot ROMs in mask ROM (such as those in many ARM SoCs).

Most x86 platforms map the firmware in SPI flash directly into address space at the reset vector, where it can be executed in-place. Prior to this, some early

initialization may be performed by the ROM microcode, or by coprocessors (such as the ME/PSP) if present. |

| Firmware Signing | None |

| CPU Microcode | Proprietary, RE possible on fam10h CPUs On K10-microarchitecture CPUs (e.g. fam10h Opterons of the 4100- and

6100-series, microcode updates are neither signed nor encrypted, and have been succesfully modified (modifying the behaviour of instructions to insert and trigger

proof-of-concept backdoors) as part of RUB-Sysstat's "Microcode" project (paper,

GitHub). On later CPUs (e.g. 6200/6300-series Opterons), microcode is encrypted. |

| Management Coprocessor: Firmware | Free (OpenBMC) |

| Communications Coprocessor: Internal Firmware | None, unless you install one |

| Communications Coprocessor: Host-Loaded Firmware | None, unless you install one |

| Security Coprocessor: Firmware | None, but has TPM header (TPM can be added) |

| Embedded Controller: Firmware | None, EC-like functions on BMC |

| Hardware: Board Electrical Schematic | Proprietary |

| Hardware: Board PCB Design | Proprietary, but boardview often available |

| Hardware: CPU Instruction Set | Proprietary (x86_64) |

| Hardware: CPU/SoC Implementation | Proprietary (AMD K10/Bulldozer/Piledriver) |

| Hardware: CPU/SoC Synthesis Toolchain | Proprietary |

Back to Table